译自原文

Temperature-dependent electrical characterizations of high-current-density AlN quasi-vertical Schottky barrier diodes on AlN substrates

原文链接

https://doi.org/10.1063/5.0317364, APL Electronic Devices 2, 016130 (2026)

原文作者

Bingcheng Da, 1 Fikadu Alema, 2 Junzhe Xie, 1 Will Brand, 2 Vitali Soukhoveev, 2 Dawei Wang, 1 Xianzhi Wei, 1 Dinusha Herath Mudiyanselage, 1,3 Andrei Osinsky, 2 and Houqiang Fu1,a)

1 School of Electrical, Computer, Energy Engineering, Arizona State University,

2Agnitron Technology, Inc.,

3 Ingarm School of Engineering, Texas State University.

项目支持方

美国国防高级研究计划局(DARPA)、美国国家科学基金会(NSF)

摘要

本研究采用金属有机化学气相沉积技术,在本征AlN单晶衬底上制备了高电流密度(>1 kA/cm²)的准垂直AlN肖特基势垒二极管。该器件表现出约2.5 V的开启电压、超过10⁷的整流比、>2.5 kA/cm²的通态电流密度以及1.5 mΩ·cm²的低比导通电阻。通过测量不同温度下的正反向偏压电流-电压特性,研究了关键器件参数及其高温漏电行为。在正向偏压下,肖特基势垒高度随温度升高而增加,理想因子则随之降低,表明金属/AlN界面存在非均匀性。本文对该肖特基势垒的非均匀特性进行了系统研究,提取的平均肖特基势垒高度为2.55 ± 0.27 eV。温度依赖的反向漏电分析表明,普尔-弗伦克尔发射与陷阱辅助隧穿是主要的漏电机理。本工作可为推进超宽禁带AlN基电子器件的发展提供有益参考。

引言

超宽禁带半导体因其宽带隙、高临界击穿电场和优异的化学稳定性,在高功率、高电压、高效率电力电子与射频电子器件以及恶劣环境工作能力方面展现出巨大潜力,近年来引起了广泛的研究兴趣。在常见超宽禁带半导体(如Ga₂O₃、金刚石、AlGaN和BN)中,氮化铝因其最大的带隙(约6.1 eV)、最高的临界击穿电场(>12 MV/cm)和较高的热导率而尤为突出,使其成为下一代功率电子器件平台的极具前景的材料。然而,迄今实现高性能AlN功率器件仍面临诸多挑战。硅常用作AlN的n型掺杂剂,但其电离能较高(约200 meV)。此外,低掺杂水平下的碳杂质与位错,以及高掺杂水平下的缺陷复合体,会进一步补偿施主并限制AlN中的自由电子浓度。同时,AlN基功率电子器件还受限于低通态电流和较差的欧姆接触。目前,AlN外延层可在高位错密度的异质衬底(如蓝宝石)上生长,也可在低位错密度(低数个数量级)的本征AlN单晶衬底上生长。高位错密度会严重制约器件性能与稳定性。尽管AlN器件仍处于发展早期,但已取得显著进展。多种AlN二极管已展现出高击穿电压等良好性能,AlN基晶体管也见诸报道。对于传统的硅基和碳化硅基功率电子器件,纵向结构因其更高的电流与电压耐受能力、更小的芯片尺寸、更好的热管理及更易扩展等优势而成为主流选择。由于缺乏商业化的导电AlN衬底,大多数已报道的AlN器件为横向结构,仅少数研究展示了纵向与准纵向AlN器件。纵向器件通常需要导电衬底以便底部接触直接位于晶圆背面(实现完全纵向电流),而准纵向器件通常在绝缘衬底上制备底部导电层,底部接触位于导电层侧边(电流以纵向为主,含少量横向分量)。Kinoshita等人首次通过衬底去除工艺,在氢化物气相外延生长的AlN上制备了完全纵向的肖特基势垒二极管,其击穿电压达550–770 V,但理想因子较高(约8)。Maeda等人利用分子束外延制备了基于AlGaN接触层的准纵向SBDs;Ran等人则在半极性AlN上通过金属有机化学气相沉积报道了类似结构,其电流密度约为1 A/cm²。近期,Quiñones等人展示了电流密度>5 kA/cm²、击穿电压约680 V、理想因子<1.2的准纵向AlN SBDs,为高性能AlN准纵向二极管的发展开辟了道路。然而,对准纵向AlN SBDs的系统性电学表征及其温度依赖特性的研究仍较为缺乏。

本工作成功制备了具有kA/cm²级电流密度的准纵向AlN SBDs,并系统研究了其在正、反向偏压下的温度依赖电学特性。 在室温下,器件展现出良好的整流特性:通态电流密度达2.5 kA/cm²,比导通电阻为1.5 mΩ·cm²,开启电压约2.5 V,整流比高达10⁷以上。在正向偏压下,温度依赖的电流-电压特性表明肖特基界面存在非均匀性,当温度从298 K升至423 K时,肖特基势垒高度从1.2 eV增加至1.68 eV,理想因子则从3.5降至2.3。在反向偏压下,通过对漏电机理的研究发现,普尔-弗伦克尔发射与陷阱辅助隧穿是器件反向漏电的主要机制。本工作可为未来AlN基电子器件的开发提供重要依据和有益参考。

实验

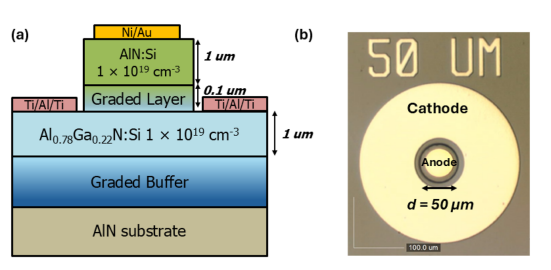

本研究的器件结构采用 Agnitron Technology 公司的 Agilis™ 100 Mini 型金属有机化学气相沉积系统制备。该结构生长于 Crystal IS 公司提供的本征(0001)面 AlN 衬底上,衬底位错密度约为 10⁴ cm⁻²。首先在衬底上沉积一层导电 AlGaN 电流扩展层,随后外延生长约 1 μm 厚的硅掺杂 AlN 层。具体制备流程如下:

将 10 × 10 mm² 的 AlN 衬底置于 90°C 的磷酸-硫酸混合溶液中进行化学清洗,经去离子水冲洗并氮气吹干后,装入反应腔。在 1250°C 下通入 NH₃ 退火约 15 分钟,以准备外延表面。

随后沉积组分渐变的 AlGaN 缓冲层:首先生长 20 周期的 3 nm AlN / 3 nm Al₀.₈₅Ga₀.₁₅N 超晶格,接着依次生长 Al 组分分别为 95%、90%、85%、80% 和 78% 的 AlGaN 层(每层约 100 nm),各层之间以约 3 nm 的 AlN 间隔层分隔。该超晶格与渐变 AlGaN 层共同构成完整的渐变缓冲层结构[图 1(a)],实现从 AlN 衬底到外延层的平稳过渡,并最大限度地降低 AlGaN/AlN 界面的应变。

在该缓冲层之上,生长约 1 μm 厚的 Si 掺杂 Al₀.₇₈Ga₀.₂₂N 层(Si 浓度约 1×10¹⁹ cm⁻³),随后沉积 100 nm 厚的 Si 掺杂 AlGaN 层,其 Al 组分从 78% 渐变至 100%。外延堆叠的最后为 1 μm 厚的 n 型 AlN 层(Si 浓度约 1×10¹⁹ cm⁻³),通过 X 射线衍射估算其位错密度约为 10⁵ cm⁻² 量级。需要说明的是,由于 AlN 中掺杂效率较低,n 型 AlN 层需进行较高浓度掺杂;然而在功率器件设计中,正向与反向特性常需折中考虑,高浓度掺杂可能对器件反向漏电产生不利影响。

在生长完整结构前,已在相同渐变缓冲层上对 Si 掺杂 Al₀.₇₈Ga₀.₂₂N 层进行了独立优化,霍尔测量显示其自由电子浓度约 6.2×10¹⁸ cm⁻³,迁移率约 38 cm²/V·s(电阻率约 26 mΩ·cm)。该优化后的生长条件随后被用于制备本结构中的渐变缓冲层。

图1. 制备的准纵向AlN肖特基势垒二极管的(a)截面示意图与(b)俯视显微图像。

图1(a)展示了所制备器件的截面结构。样品在本征AlN单晶衬底上通过同质外延生长,并采用梯度缓冲层以缓解外延层与衬底之间的晶格失配。外延结构由生长在n-Al₀.₇₈Ga₀.₂₂N接触层上的n-AlN层构成。其间插入了100 nm的渐变AlGaN层,旨在降低势垒并增强n-AlN层与n-AlGaN接触层之间的电流传输,尽管该渐变层也可能引入极化电荷。制备工艺采用标准光刻与剥离步骤。首先使用基于氯气的BCl₃/Cl₂电感耦合等离子体刻蚀去除顶部AlN层和渐变层,以便在AlGaN层上制备欧姆接触,并形成深度约1.3 μm的台面结构。刻蚀所用的ICP功率和RF功率分别为400 W和70 W,刻蚀速率约为200 nm/min。随后通过电子束蒸发沉积Ti/Al/Ti金属叠层,并在氮气环境中进行950°C、60秒的快速热退火,以形成欧姆接触。基于圆形传输线模型测量的欧姆接触电阻率提取值为4.9×10⁻³ Ω·cm²。最后,通过电子束蒸发沉积Ni/Au金属叠层形成肖特基接触。图1(b)展示了器件的俯视光学显微图像。阳极直径为50 μm,阳极与阴极之间的台面边缘间距为10 μm。制备完成的器件的电流-电压与电容-电压特性测量使用配备热台的探针台和Keithley 4200 SCS半导体分析仪完成。

结果与讨论

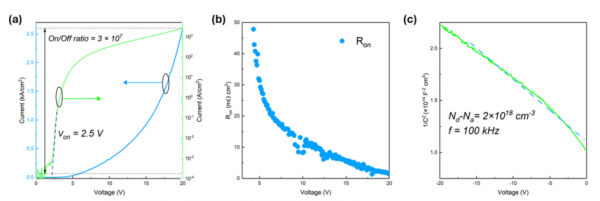

图2(a)展示了器件在室温下测得的前向I-V特性。该肖特基势垒二极管的最大通态电流密度超过2.5 kA/cm²,开启电压约为2.5 V,整流比高达约3×10⁷。从I-V曲线进一步提取的微分导通电阻如图2(b)所示,在20 V时获得最低值1.5 mΩ·cm²。如此低的导通电阻与kA级的电流密度,证明了渐变缓冲层在降低AlN/AlGaN界面电子势垒方面的有效性。此外,在100 kHz频率下进行了电容-电压测试。选用该相对较低的频率有助于降低串联电阻的影响。图2(c)显示了1/C²-V关系曲线,据此提取的有效净电荷浓度约为2×10¹⁸ cm⁻³。值得注意的是,该值低于标称的Si掺杂浓度,这主要归因于Si施主因其高激活能而导致的不完全电离²⁹,以及掺杂补偿效应。

图2. 准纵向AlN肖特基势垒二极管的(a)线性坐标与半对数坐标下的正向I-V特性曲线;(b)提取的器件微分导通电阻RON随电压的变化关系;(c)器件的C-V特性(1/C²-V关系图)。

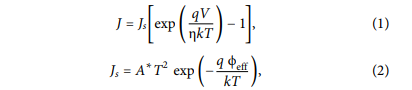

为评估器件在高温下的性能,我们进行了温度依赖的I-V特性测试,结果如图3(a)所示。采用热电子发射(TE)模型提取了准纵向SBDs的肖特基势垒高度(φeff)与理想因子(η)。TE模型可表述为:

其中,J为电流密度,Js为饱和电流密度,A∗为理查森常数,T为温度(单位:K),q为电子电荷,ϕeff为有效肖特基势垒高度,η为理想因子,k为玻尔兹曼常数,m∗为电子有效质量,h为普朗克常数。在本工作中,计算中采用的 A∗=57.7A⋅cm−2⋅K−2,电子有效质量取 0.48m0。提取的势垒高度 ϕb与理想因子 η随温度的变化关系如图3(b)所示。两个参数均表现出明显的温度依赖性:从室温升至423 K时,ϕeff从1.2 eV增加至1.68 eV,η则从3.5降至约2.3。在AlN SBDs中观察到较高的理想因子较为常见,通常归因于寄生电流传导机制。进一步将 η与 ϕeff的关系绘制于图3(c),可见其呈线性相关,这通常归因于金属/半导体界面的非均匀性导致肖特基势垒高度分布不均。在较低温度下,电子倾向于穿越低势垒区域;而在较高温度下,热激活电子能够克服更高势垒。这种非均匀特性可能源于肖特基接触与半导体间的界面粗糙度、冶金不均匀性及金属晶界等因素。肖特基势垒高度可视为服从高斯分布的势能起伏,其平均势垒高度为 ϕb,标准偏差为 σ,可表示为:

其中,ϕb0与 σ0为零偏压下的值,系数 γ与 ξ表示电压引起的肖特基势垒分布形变。根据该关系,有效肖特基势垒高度 ϕeff与 q/kT呈线性函数关系,这已在图3(d)中得到验证。由此提取的平均势垒高度为 2.55±0.27eV,与Ni/AlN势垒高度的理论预测值(约2.2 eV)基本一致。

图3. 准纵向AlN肖特基势垒二极管的 (a) 温度依赖正向I-V特性;(b) 理想因子与肖特基势垒高度随温度的变化关系;(c) 肖特基势垒高度与理想因子的关系;(d) 肖特基势垒高度随 q/kT 的变化关系。

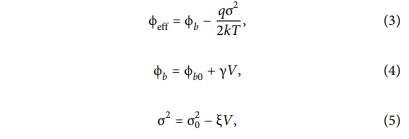

图4(a)展示了准纵向AlN肖特基势垒二极管的温度依赖反向I-V特性。可观察到两个明显不同的区域:在反向偏压低于7.5 V时,器件I-V曲线随温度变化显著;而在更高反向偏压下,不同温度下的I-V曲线开始相互重叠。需要说明的是,在448 K的I-V曲线中,约-6 V处出现的微弱漏电流下降属于测量装置轻微振动引起的假象。图4(b) 更清晰地展示了这两个不同区域,其中电流密度以1000/T的函数形式在不同反向偏压下绘制。在低反向偏压的区域A,漏电流表现出强烈的温度依赖性,这体现在阿伦尼乌斯曲线陡峭的斜率上;而在高反向偏压的区域B,漏电流则呈现温度依赖性极弱的平坦特性。该现象可归因于AlN肖特基势垒二极管中存在的不同漏电机理。图4(c) 展示了AlN肖特基势垒二极管中可能存在的反向漏电机理。由于AlN肖特基势垒二极管具有较大的肖特基势垒高度(>1 eV),热电子发射与热场发射受到抑制,使其对反向漏电流的贡献较小。因此,通常需要考虑其他机理,如图4(c)所示的普尔-弗伦克尔发射、陷阱辅助隧穿、福勒-诺德海姆隧穿、场发射及变程跳跃等。为确定本工作中的主导机理,我们采用与这些过程对应的数学模型对反向漏电流进行了拟合,各漏电机理的具体表达式可参考文献。

图4. 准纵向AlN肖特基势垒二极管的 (a) 温度依赖反向I-V特性;(b) 不同偏压下反向电流密度与1000/T的函数关系;(c) AlN SBDs中可能的漏电机理示意图。

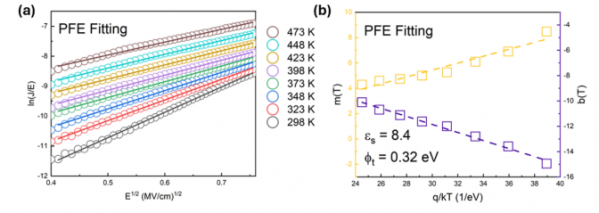

图5. (a)准纵向AlN肖特基势垒二极管在不同温度下实验数据的 ln(J/E) 与 E¹/² 关系及其拟合曲线;(b)由(a)中拟合参数所得截距 b(T) 和斜率 m(T) 随温度的变化关系。

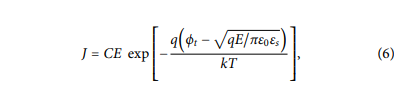

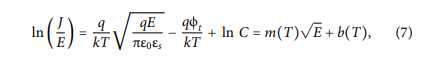

在区域A中,log J 与1/T呈线性关系,该特征在所有考虑的漏电机理中仅对应普尔-弗伦克尔发射过程。PFE是一种陷阱辅助的传输机制,其载流子密度与陷阱活化能呈指数关系。PFE引起的电流密度可表达为:

其中,E为有效电场,ϕt为电子从陷阱态发射的势垒高度,εs为相对介电常数,ε0为真空介电常数,C为比例常数,k为玻尔兹曼常数。在高电场作用下,原本局域于陷阱位置的电子可被激发至导带,从而形成反向漏电流。进入导带后,这些电子可能在半导体中漂移,直至被其他陷阱重新捕获。换言之,PFE模型描述了电场增强的陷阱态发射过程,该过程导致反向漏电流增大。

将上述方程改写后,ln(J/E)与 E1/2呈线性关系:

剩余原文请至【奥趋光电】微信公众号查看