原文标题

Pushing the power envelope — Novel designs enrich the performance of power devices employing a range of semiconducting materials

原文作者

Richard Stevenson, Editor, CS MAGAZINE

全文链接

https://data.angel.digital/pdf/Compound_Semiconductor_Issue_1_2024.pdf#page=28

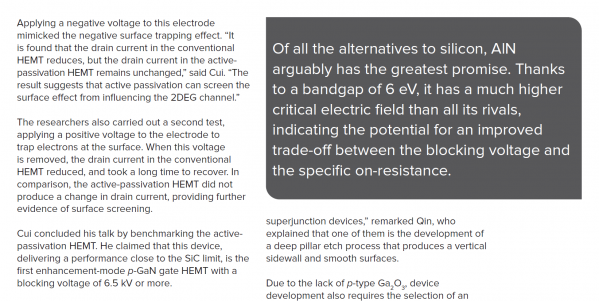

在硅的所有替代品中,可以说AlN(氮化铝)具有最大的潜力。由于具有6 eV的带隙,它的临界电场远高于所有竞争对手,这表明它有可能在阻断电压和特定导通电阻之间实现更好的权衡。

GaN和SiC等还只是具有潜力的材料时代早已一去不复返了。现在,它们正在发挥自己的潜力,其显著的商业成功就是证明。由于在电动汽车中的广泛应用,SiC MOSFET的销量正在飙升,而GaN现已成为制造便携式设备快速充电器的材料。

但是,电力电子技术的革命还没有结束。在几千伏或更高电压下工作时,主流器件仍然是硅基IGBT和晶闸管。然而,一些基于化合物半导体材料的新型替代器件正在取代它们--它们也可以在更低的电压下发挥作用。

在2023年12月9日至13日于加利福尼亚州旧金山举行的久负盛名的IEEE国际电子器件会议(IEDM)上,出现了这些器件的几个杰出代表。会上讨论了许多进展,包括:首次展示了6.5kV沟槽形SiC IGBT;GaN HEMT能够阻断电同时提供超低动态导通电阻;首款由Ga2O3制成的击穿电压达2kV垂直超结器件;基于AlN的垂直p-n二极管,采用非掺杂剂掺杂的分布式极化掺杂,其临界电场几乎是所报道的SiC和GaN值的两倍。

沟槽型SiC IGBT

各国为减少碳足迹所做的努力需要包括引入智能电网和高压直流输电系统。这两项创新的基础包括静态同步补偿器和固态变压器,它们是由能够耐高电压、提供大电流的功率器件组成。

由SiC制成的器件有望成为这些补偿器和变压器的候选器件。SiC不仅能确保器件的高性能,还能在高频率下工作,这为缩小补偿器和变压器的尺寸、提高其效率打开了大门。不过,如果采用6.5kV SiC MOSFET,导通电阻是一个令人担忧的问题,尤其是在温度较高的情况下--在175°C时,导通电阻为104 mΩcm2。

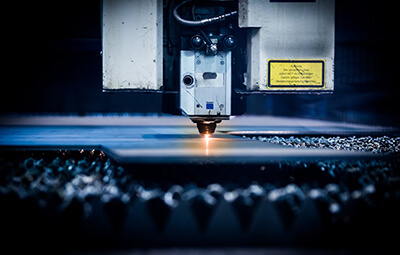

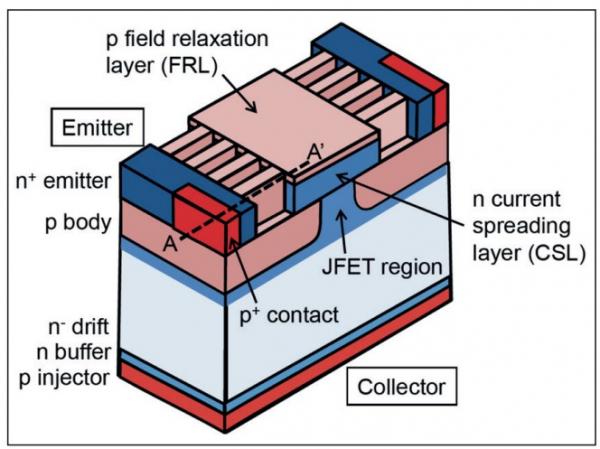

由于这一限制,许多研究小组已经开发出了SiCIGBT。其中包括利用厚漂移层实现耐15 kV电压的产品,以及日立公司首创的变体,其特点是采用更薄的漂移层来降低开关损耗。2016年,日立公司的研究人员推出了采用极薄漂移层的6.5 kV低开关损耗SiC IGBT,在最近的IEDM上,该团队又推出了采用沟槽蚀刻双扩散MOS结构的后代产品(见图1),旨在解决因沟道迁移率低而导致的发射极电子注入低的问题。

图1.采用沟槽蚀刻双扩散MOS结构的n沟道SiC IGBT

Naoki Watanabe在他的IEDM演讲中描述了这种器件,并强调了传统SiC沟槽栅极结构的一个弱点:"在沟槽底部,由于SiC的临界电场很高,而SiC的临界电场靠近栅极氧化物,因此在关断状态下栅极氧化物中会产生高电场。因此,要实现沟槽栅SiC IGBT,电场弛豫是必要的。

为解决这一问题,该团队开发了一种新颖的SiC IGBT,采用沟槽蚀刻双扩散MOS结构。据称,这种采用V型结构的设计的优点之一是通过缩小沟槽间距提高了沟道密度。另一个优点是,在关态工作时,通过将沟槽埋入p体,栅极氧化物中的电场大幅度降低。

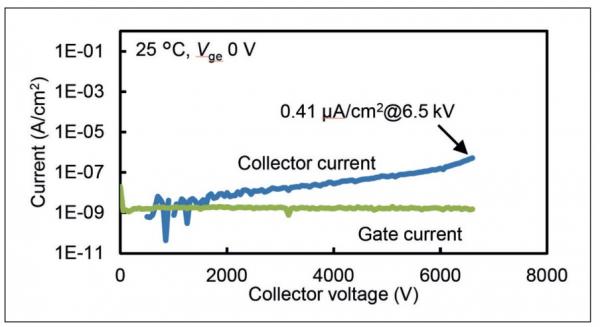

图2.采用沟槽蚀刻双扩散MOS结构的SiC IGBT可实现超过6.5 kV的阻断电压

为了评估沟槽蚀刻双扩散MOS结构的能力,Watanabe及其合作者制作了这种形式的测试结构,然后将其电气特性与平面变体进行了比较。在绘制栅极电压与漏极电流的函数关系图时发现,沟槽蚀刻双扩散MOS结构的电流增加了一倍,这要归功于鳍状结构。Watanabe认为:"因此,沟槽蚀刻双扩散MOS结构可以增强发射极的电子注入。“

研究小组的模拟研究深入了解了该器件在关断状态下的电场,其峰值为2 MVcm-1。Watanabe说:"这个值很低,足以确保高可靠性。"他还补充说,沟槽蚀刻双扩散MOS结构抑制了栅极氧化物中的电场。该团队的新型IGBT的制备过程始于使用n+衬底并沉积包括70 μm漂移层的外延结构。通过使用背面研磨作为最后一道工序,制备出了漂移层很薄的IGBT。

电气特性测量结果显示,采用沟槽蚀刻双扩散MOS结构的IGBT的导通电压(定义为集电极电流为200 Acm-2时的电压)为4.8 V,而平面型器件的导通电压为6.7 V。接通时,新型IGBT的差分导通电阻为6.6 mΩcm2,约为平面器件的三分之一。采用沟槽蚀刻双扩散MOS结构的IGBT在6.5kV电压下的集电极漏电流为0.41 mAcm-2(见图2),证明了它的阻断能力。

采用沟槽蚀刻双扩散MOS结构的IGBT开关特性也优于平面型器件。由于反馈电容较小,发射极的电子注入量较大,关闭和开通损耗分别降低了约19%和6%。

有源钝化GaN HEMT

在IEDM上展出的另一款器件是E-mode有源钝化p-GaN栅极HEMT,它能够提供6.5 kV的阻断电压,并且目标市场是未来的电网基础设施。

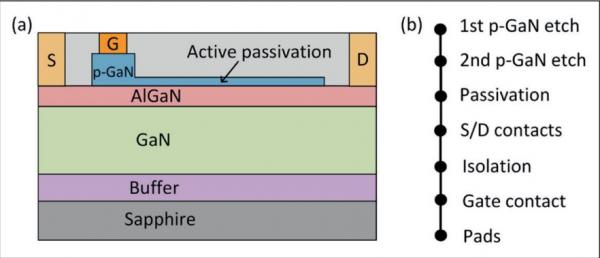

图3.有源钝化HEMT的结构(a)及其制备工艺概要(b)

这种在蓝宝石衬底上生长的横向GaN HEMT由北京大学、清华大学和名古屋大学的研究人员合作开发,其优点包括不需要厚外延结构,并有机会将同一外延片用于低压和高压器件。北京大学的崔嘉伟代表团队发言时指出,开发千伏级GaN功率开关时面临的两大挑战是确保E-mode模式工作(即器件通常处于关闭状态)和动态导通电阻的稳定性。"p-GaN栅极HEMT是E-mode GaN功率晶体管的主流技术。"为了充分利用过去几年积累的经验,我们认为将p-GaN栅极结构用于高压晶体管也是一个不错的选择"。

为了抑制动态导通电阻,崔和合作者放弃了添加多个场板的传统方法,因为这种方法对于工作电压超过几千伏的设备来说是不切实际的。

"作为一种替代方案,我们提出了有源钝化p-GaN栅极HEMT,"崔解释说,在这种晶体管中,减薄的p-GaN层提供了钝化功能(见图3)。这种形式的HEMT还具有其他特点,如可以屏蔽移动空穴的表面捕获,以及只需一个额外步骤就能实现有源钝化。

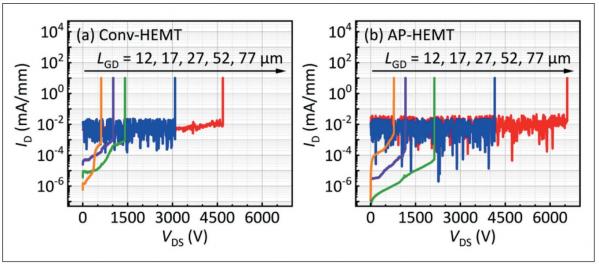

图4.传统GaN HEMT(a)的关态特性不如采用有源钝化设计的变体(b)

制作该团队的器件时,首先采用传统的外延片,该外延片具有高电阻率缓冲层、200 nm厚的未掺杂GaN沟道、15 nm厚的Al0.2Ga0.8N势垒和20 nm厚的p-GaN盖,并通过两步工艺选择性地蚀刻到该层中。然后沉积SiO2使器件钝化,再加入欧姆触点、隔离步骤以及形成栅极触点和探针垫。

电学测量显示,有源钝化HEMT器件与传统HEMT器件相比具有优异的关态阻断能力。对于这两种器件,栅极长度的增加会导致更高的阻断电压,栅极长度为77μm的有源钝化HEMT能够阻断6.573 kV的电压(见图4)。研究小组认为,有源钝化HEMT的阻断电压之所以更高,是因为耗尽区的位置发生了变化,不再部分位于栅极下方。根据对传输电流电压特性的测量,这两种形式的HEMT都呈现出E-mode模式工作,阈值电压为0.8 V。对输出电流-电压特性的测量结果表明,带有源钝化的HEMT的导通电阻低于对比组,分别为38.2 mWmm和43.6 mWmm。

为了评估其器件的动态导通电阻,崔和同事比较了一系列漏极-源极电压下的动态值和静态值。据报道,在4.5 kV电压下对栅极长度为77μm E-mode模式p-GaN栅极HEMT进行测量时,该比率很低,为1.02。据称,出色的导通电阻特性源于钝化层的屏蔽效应。为了验证这一归因,研究小组制作了一对器件--有有源钝化层和无源钝化层,其中包括一个表面测试电极。在该电极上施加负电压可模拟负表面陷阱效应。"崔说:"我们发现,传统HEMT中的漏极电流减小了,但有源钝化HEMT中的漏极电流保持不变。"这一结果表明,有源钝化可以屏蔽表面效应对2DEG沟道的影响"。

研究人员还进行了第二项测试,在电极上施加正电压,在表面捕获电子。去掉电压后,传统HEMT的漏极电流减小,需要很长时间才能恢复。相比之下,有源钝化HEMT的漏极电流没有变化,进一步证明了表面屏蔽的作用。

最后,崔介绍了有源钝化HEMT。他声称,该器件的性能接近SiC的极限,是首个阻塞电压达到或超过6.5 kV的E-mode p-GaN栅极HEMT。

Ga2O3超级结肖特基整流器

另一项新突破来自美国和日本研究人员的合作:用超宽带隙材料Ga2O3制成的首个垂直超结器件。弗吉尼亚理工学院和州立大学、南加州大学、美国海军研究实验室、Novel Crystal Technology和橡树岭国家实验室的研究人员通过合作,开发出了一系列具有1-2 μm宽、包裹着电荷平衡对型的p型NiO柱器件。这些器件耐压可高达2kV。

来自弗吉尼亚理工学院和州立大学的Yuan Qin代表合作伙伴发言,他首先强调了Ga2O3的优势。这些优势包括临界电场高(预计可达8 MVcm-1)、高温稳定性以及在大直径基底上外延生长的可能性。遗憾的是,这种氧化物有两大缺点:缺乏p型掺杂和热导率低。Qin简要介绍了各种形式半导体器件的演变过程,并解释说,从一维结构到多维变体(如采用超结、多通道和多栅极的器件)的转变,在系统层面实现了更高的功率密度和效率。对于超结器件(如Qin及其同事制备的器件),导通电阻随阻塞电压呈线性增长,而对于一维器件,导通电阻则随阻塞电压的平方而变化。

Qin说:"对于超宽带隙半导体氧化镓来说,制备超结器件仍面临一些挑战,"他解释说,其中一个挑战是开发一种能产生垂直侧壁和光滑表面的深柱蚀刻工艺。由于缺乏p型Ga2O3,器件开发还需要选择一种不会导致过多界面陷阱的可替代的p型材料。NiO显然是一个候选材料--它曾被用于制备GaN中的垂直超结和Ga2O3中的横向超结。

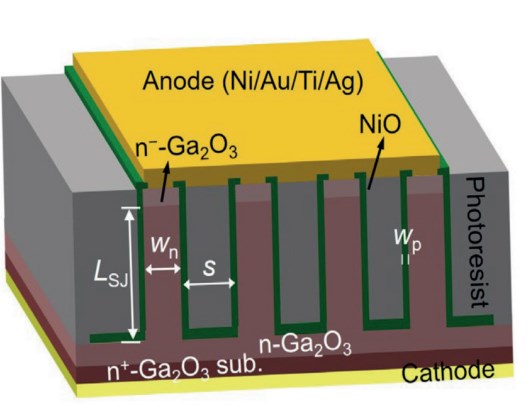

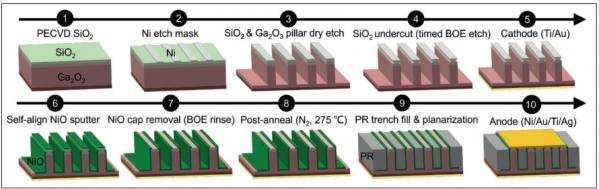

超结器件的制备涉及对NCT生产的2英寸Ga2O3外延片的处理,该外延片有10μm厚的n-Ga2O3层(掺杂水平为2x1017cm-3)和0.5μm厚的n-Ga2O3层(掺杂水平为1x1016cm-3)。干法蚀刻产生了6.5μm深的柱子,在氩气和氧气环境中通过共形溅射(conformal sputtering)将其包裹在NiO中。由于NiO中的受主浓度远高于Ga2O3柱中的施主浓度,因此厚度为120 nm的NiO可以与1-2 μm宽的柱子实现电荷平衡。研究小组通过在沟槽中填充光刻胶并添加Ni/Au/Ti/Ag肖特基触点,完成了器件的制备(器件结构见图5,工艺流程详情见图6)。

图5.垂直Ga2O3超结肖特基势垒二极管的特性由沟道深度(LSJ)、沟道宽度(Wn)、沟道间距(S)和NiO厚度(Wp)等关键尺寸决定

图6.制备Ga2O3超结肖特基势垒二极管的十个步骤

在这种设计中,0.5 μm厚的顶部n-Ga2O3层有两个作用:降低肖特基触点的隧穿漏电流;将峰值电场的位置从肖特基触点转移到体超结。Qin及其合作者评估了具有各种柱宽的超结器件的阻断能力。他们发现,击穿电压最初随支柱宽度的增加而增加,在支柱宽度为1.8 mm时达到2kV,而在更宽的支柱宽度时则有所下降。峰值阻断能力源于最佳电荷平衡。当器件温度升高到175℃时,研究小组观察到阻断电压略微降低到1.8 kV。这表明,电荷平衡在高温下得以保持。对于具有最佳阻断电压的器件,室温下的导通电压为1 V,导通-关闭比约为109,导通电阻仅为0.7 ΩWcm2。在175°C时,开启电压降至0.8 V,导通比率约为108,导通电阻为1.3 ΩWcm2。

在对该器件进行基准测试后,Qin指出,在600V至4kV的所有肖特基势垒二极管和结势垒肖特基二极管中,该器件在特定导通电阻和击穿电压之间实现了最佳折中。该团队的器件可提供快速开关,其性能接近GaN的一维极限。

AlN垂直p-n型二极管

在硅的所有替代品中,可以说AlN(氮化铝)具有最大的潜力。由于具有6 eV的带隙,它的临界电场远高于所有竞争对手,这表明它有可能在阻断电压和特定导通电阻之间实现更好的权衡。

多年来,AlN器件的缺点之一就是缺乏原生衬底。不过,近年来我们已经取得了很大进展,2022年的报告显示,这种材料中的穿线位错密度可低于104 cm-2,旭化成公司也于2023年宣布推出直径为4英寸的单晶衬底。

氮化铝的另一个问题是难以实现导电层。由于常见掺杂剂的电离能较高,硅施主的电离能为282 meV,镁受主的电离能为630 meV,因此通过传统方法实现室温导电是一项挑战。加州大学圣巴巴拉分校在20多年前首创的分布式极化掺杂法提供了一种解决方案。通过使用取决于分级方向的正或负固定空间电荷,可以在氮化物化合物中实现p型和n型导电性。在这种方法的基础上,名古屋大学和旭化成的研究小组利用分布式极化掺杂法在AlN基激光二极管中产生了一个p型层。据说,这种生产p型层的方法可以提高注入效率,减小串联电阻,最终实现在紫外线下连续发射激光。

在IEDM会议上,该团队宣布在分布式极化掺杂方面取得了进一步的成功,利用这种方法在基于AlN的垂直p-n二极管中生产出了p型和n型层。来自名古屋大学的Takeru Kumabe向IEDM代表解释说,在他们的团队最近取得成功之前,铝成分超过30%的AlGaN二极管还没有表现出理想的电气特性。

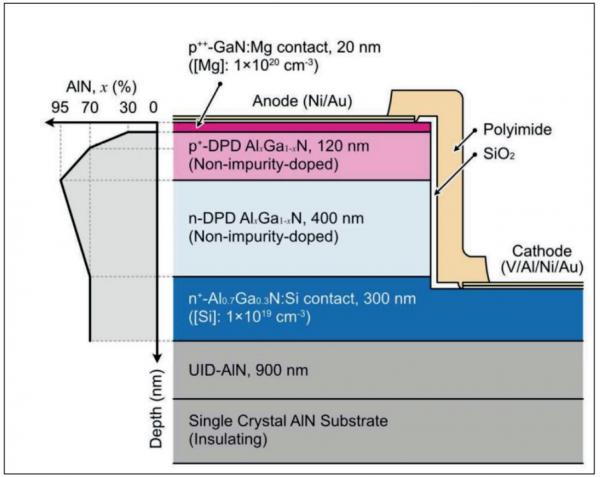

Kumabe及其合作者制作器件的方法是,在AlN基底上生长出300 nm厚的Al0.7Ga0.3N接触层,然后是400 nm厚的分布式极化掺杂AlGaN n型层、120 nm厚的分布式极化掺杂p型层,最后是20 nm厚的镁掺杂GaN接触层。在分布式极化掺杂层中,AlGaN层的铝含量从70%到95%不等。

图7.分布式极化掺杂用于形成AlN基二极管

二极管的制备始于封盖层中镁掺杂剂的活化。在添加阴极、阳极和接触垫以及防止空气放电的聚酰亚胺表面保护层之前,蚀刻工艺确定了垂直mesa结构,等离子体增强CVD提供了SiO2保护层。

二次离子质谱(SIMS)测定的负电荷和正电荷浓度平均值分别为1.8x1018 cm-3和2.6x1017 cm-3。"Kumabe解释说:"在这两个分布式极化掺杂层中,电荷浓度沿深度方向恒定不变,这要归功于线性成分分级。并补充说,SIMS和X射线RSM图的结果表明,该结构符合预期设计。在室温下对二极管进行的电气测量显示,其导通电压为6.5 V,比导通电阻为3 mΩcm2。据Kumabe称,这是迄今所报道的AlN基p-n二极管的最小比导通电阻值。

研究小组还利用电致发光(EL)来仔细研究其器件的运行。Kumabe说:“EL发射随着电流的增加而增加,这表明电子和空穴都对典型p-n二极管的传导做出了贡献。“

为了验证他们的器件是否是真正的p-n二极管,Kumabe及其合作者在323 K至573 K的温度范围内测量了电流密度与正向偏压的函数关系,发现阈值电压随着温度的升高而降低。使用重组电流模型来描述电学行为进一步证明了该团队的器件表现为p-n二极管,而不是具有金属-绝缘体-半导体结构的器件(见图8)。

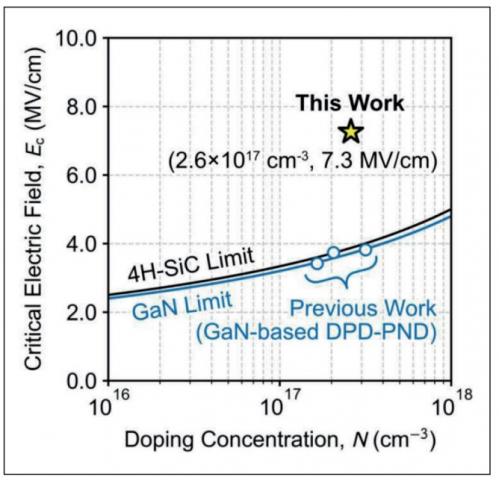

反向偏压测量显示,器件在-283 V发生破坏性击穿,这表明雪崩击穿并未发生。因此,Kumabe及其合作者计算出击穿时的电场强度为7.3 MVcm-1。Kumabe说:"提取的电场与SiC和GaN电场极限以及之前报道的分布式极化掺杂GaNp-n二极管进行了比较。7.3 MVcm-1的数值几乎是相同掺杂浓度下GaN和SiC极限值的两倍。“

图8 AlN二极管随温度变化的理想因子接近2,这表明电子和空穴在器件运行中都发挥了作用

图9.采用分布式极化掺杂的AlN基二极管的性能远远超过了SiC和GaN的极限

Kumabe还指出,他们的设备打破了GaN衬底上分布式极化掺杂GaN二极管所能实现的极限。"Kumabe总结说:这一结果证明了氮化铝和高铝含量AlGaN在功率器件应用中的巨大潜力。“

这些工作表明,AlN器件正在取得巨大进步。除了在IEDM和其他会议上报告的SiC、GaN和Ga2O3器件的进展之外,毫无疑问,电力电子器件的革命正在顺利进行,但更多的进展还在后面。

原文源于【IEDM】

(以上文章由奥趋光电翻译,如有涉及版权等问题,请联系我们以便处理)